System on a chip

A system on a chip or system-on-chip (SoC functions (otherwise it may be considered on a discrete application processor).

Higher-performance SoCs are often paired with dedicated and physically separate memory and secondary storage (such as

An SoC integrates a

Compared to a multi-chip architecture, an SoC with equivalent functionality will have reduced

SoCs are very common in the

Types

In general, there are three distinguishable types of SoCs:

- SoCs built around a microcontroller,

- SoCs built around a microprocessor, often found in mobile phones;

- Specialized application-specific integrated circuit SoCs designed for specific applications that do not fit into the above two categories.

Applications

SoCs can be applied to any computing task. However, they are typically used in mobile computing such as tablets, smartphones, smartwatches and netbooks as well as embedded systems and in applications where previously microcontrollers would be used.

Embedded systems

Where previously only microcontrollers could be used, SoCs are rising to prominence in the embedded systems market. Tighter system integration offers better reliability and

Mobile computing

- ARM

- Qualcomm:

- list), used in many smartphones. In 2018, Snapdragon SoCs were being used as the backbone of laptop computers running Windows 10, marketed as "Always Connected PCs".[8][9]

- MediaTek, typically based on ARM

- Dimensity & Kompanio Series. Standalone application & tablet processors that power devices such as Amazon Echo Show

Personal computers

In 1992,

Tablet and laptop manufacturers have learned lessons from embedded systems and smartphone markets about reduced power consumption, better performance and reliability from tighter

Structure

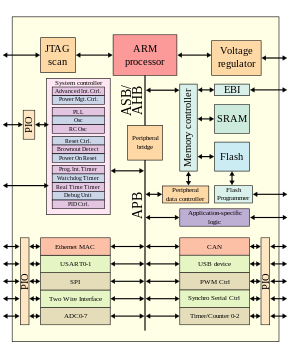

An SoC consists of hardware

Functional components

Processor cores

An SoC must have at least one

Memory

SoCs must have

Interfaces

SoCs include external

When needed, SoCs include analog interfaces including analog-to-digital and digital-to-analog converters, often for signal processing. These may be able to interface with different types of sensors or actuators, including smart transducers. They may interface with application-specific modules or shields.[nb 1] Or they may be internal to the SoC, such as if an analog sensor is built in to the SoC and its readings must be converted to digital signals for mathematical processing.

Digital signal processors

Typical DSP instructions include

Other

As with other computer systems, SoCs require

SoC peripherals including counter-timers, real-time timers and power-on reset generators. SoCs also include voltage regulators and power management circuits.

Intermodule communication

SoCs comprise many

Bus-based communication

Historically, a shared global computer bus typically connected the different components, also called "blocks" of the SoC.[13] A very common bus for SoC communications is ARM's royalty-free Advanced Microcontroller Bus Architecture (AMBA) standard.

Wire delay is not scalable due to continued

Network on a chip

In the late 2010s, a trend of SoCs implementing

Networks-on-chip have advantages including destination- and application-specific

Many SoC researchers consider NoC architectures to be the future of SoC design because they have been shown to efficiently meet power and throughput needs of SoC designs. Current NoC architectures are two-dimensional. 2D IC design has limited floorplanning choices as the number of cores in SoCs increase, so as three-dimensional integrated circuits (3DICs) emerge, SoC designers are looking towards building three-dimensional on-chip networks known as 3DNoCs.[13]

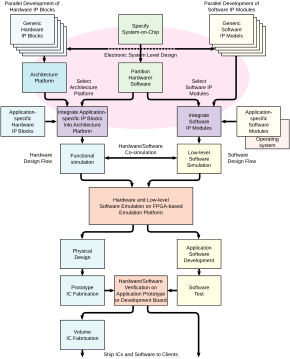

Design flow

This section needs additional citations for verification. (March 2017) |

A system on a chip consists of both the hardware, described in § Structure, and the software controlling the microcontroller, microprocessor or digital signal processor cores, peripherals and interfaces. The design flow for an SoC aims to develop this hardware and software at the same time, also known as architectural co-design. The design flow must also take into account optimizations (§ Optimization goals) and constraints.

Most SoCs are developed from pre-qualified hardware component

SoCs components are also often designed in

Once the architecture of the SoC has been defined, any new hardware elements are written in an abstract hardware description language termed register transfer level (RTL) which defines the circuit behavior, or synthesized into RTL from a high level language through high-level synthesis. These elements are connected together in a hardware description language to create the full SoC design. The logic specified to connect these components and convert between possibly different interfaces provided by different vendors is called glue logic.

Design verification

Chips are verified for validation correctness before being sent to a

Traditionally, engineers have employed simulation acceleration, emulation or prototyping on reprogrammable hardware to verify and debug hardware and software for SoC designs prior to the finalization of the design, known as tape-out. Field-programmable gate arrays (FPGAs) are favored for prototyping SoCs because FPGA prototypes are reprogrammable, allow debugging and are more flexible than application-specific integrated circuits (ASICs).[18][19]

With high capacity and fast compilation time, simulation acceleration and emulation are powerful technologies that provide wide visibility into systems. Both technologies, however, operate slowly, on the order of MHz, which may be significantly slower – up to 100 times slower – than the SoC's operating frequency. Acceleration and emulation boxes are also very large and expensive at over US$1 million.[citation needed]

FPGA prototypes, in contrast, use FPGAs directly to enable engineers to validate and test at, or close to, a system's full operating frequency with real-world stimuli. Tools such as Certus[20] are used to insert probes in the FPGA RTL that make signals available for observation. This is used to debug hardware, firmware and software interactions across multiple FPGAs with capabilities similar to a logic analyzer.

In parallel, the hardware elements are grouped and passed through a process of logic synthesis, during which performance constraints, such as operational frequency and expected signal delays, are applied. This generates an output known as a netlist describing the design as a physical circuit and its interconnections. These netlists are combined with the glue logic connecting the components to produce the schematic description of the SoC as a circuit which can be printed onto a chip. This process is known as place and route and precedes tape-out in the event that the SoCs are produced as application-specific integrated circuits (ASIC).

Optimization goals

SoCs must optimize

Common optimization targets for SoC designs follow, with explanations of each. In general, optimizing any of these quantities may be a hard

For broader coverage of trade-offs and requirements analysis, see requirements engineering.

Targets

Power consumption

SoCs are optimized to minimize the

Performance per watt

SoCs are optimized to maximize

Waste heat

SoC designs are optimized to minimize waste heat output on the chip. As with other integrated circuits, heat generated due to high power density are the bottleneck to further miniaturization of components.[21]: 1 The power densities of high speed integrated circuits, particularly microprocessors and including SoCs, have become highly uneven. Too much waste heat can damage circuits and erode reliability of the circuit over time. High temperatures and thermal stress negatively impact reliability, stress migration, decreased mean time between failures, electromigration, wire bonding, metastability and other performance degradation of the SoC over time.[21]: 2–9

In particular, most SoCs are in a small physical area or volume and therefore the effects of waste heat are compounded because there is little room for it to diffuse out of the system. Because of high

These thermal effects force SoC and other chip designers to apply conservative

Throughput

This section needs expansion. You can help by adding to it. (October 2018) |

SoCs are optimized to maximize computational and communications

Latency

This section needs expansion. You can help by adding to it. (October 2018) |

SoCs are optimized to minimize latency for some or all of their functions. This can be accomplished by laying out elements with proper proximity and locality to each-other to minimize the interconnection delays and maximize the speed at which data is communicated between modules, functional units and memories. In general, optimizing to minimize latency is an NP-complete problem equivalent to the boolean satisfiability problem.

For tasks running on processor cores, latency and throughput can be improved with task scheduling. Some tasks run in application-specific hardware units, however, and even task scheduling may not be sufficient to optimize all software-based tasks to meet timing and throughput constraints.

Methodologies

This section needs expansion. You can help by adding to it. (October 2018) |

Systems on chip are modeled with standard hardware verification and validation techniques, but additional techniques are used to model and optimize SoC design alternatives to make the system optimal with respect to multiple-criteria decision analysis on the above optimization targets.

Task scheduling

Task scheduling is an important activity in any computer system with multiple processes or threads sharing a single processor core. It is important to reduce § Latency and increase § Throughput for embedded software running on an SoC's § Processor cores. Not every important computing activity in a SoC is performed in software running on on-chip processors, but scheduling can drastically improve performance of software-based tasks and other tasks involving shared resources.

Software running on SoCs often schedules tasks according to

Pipelining

Hardware and software tasks are often pipelined in

Probabilistic modeling

SoCs are often analyzed though

Markov chains

SoCs are often modeled with Markov chains, both discrete time and continuous time variants. Markov chain modeling allows asymptotic analysis of the SoC's steady state distribution of power, heat, latency and other factors to allow design decisions to be optimized for the common case.

Fabrication

This section needs additional citations for verification. (March 2017) |

SoC chips are typically

When all known bugs have been rectified and these have been re-verified and all physical design checks are done, the physical design files describing each layer of the chip are sent to the foundry's mask shop where a full set of glass lithographic masks will be etched. These are sent to a wafer fabrication plant to create the SoC dice before packaging and testing.

SoCs can be fabricated by several technologies, including:

- ASIC

- Standard cell ASIC

- Field-programmable gate array (FPGA)

ASICs consume less power and are faster than FPGAs but cannot be reprogrammed and are expensive to manufacture. FPGA designs are more suitable for lower volume designs, but after enough units of production ASICs reduce the total cost of ownership.[23]

SoC designs consume less power and have a lower cost and higher reliability than the multi-chip systems that they replace. With fewer packages in the system, assembly costs are reduced as well.

However, like most

When it is not feasible to construct an SoC for a particular application, an alternative is a

Examples

Some examples of systems on a chip are:

- Apple A series

- Cell processor

- Adapteva's Epiphany architecture

- Xilinx Zynq UltraScale

Benchmarks

This section needs expansion. You can help by adding to it. (October 2018) |

SoC research and development often compares many options. Benchmarks, such as COSMIC,[25] are developed to help such evaluations.

See also

- Chiplet

- List of system on a chip suppliers

- Post-silicon validation

- ARM architecture family

- RISC-V

- Single-board computer

- System in a package

- Network on a chip

- Cypress PSoC

- Application-specific instruction set processor (ASIP)

- Platform-based design

- Lab-on-a-chip

- Organ-on-a-chip in biomedical technology

- Multi-chip module

- Parallel computing

- ARM big.LITTLE co-architecture

- Hardware acceleration

Notes

- ^ In embedded systems, "shields" are analogous to expansion cards for PCs. They often fit over a microcontroller such as an Arduino or single-board computer such as the Raspberry Pi and function as peripherals for the device.

References

- ^ Shah, Agam (January 3, 2017). "7 dazzling smartphone improvements with Qualcomm's Snapdragon 835 chip". Network World.

- Conde Nast. Retrieved December 17, 2023.

- ^ Pete Bennett, EE Times. "The why, where and what of low-power SoC design." December 2, 2004. Retrieved July 28, 2015.

- ^ Nolan, Stephen M. "Power Management for Internet of Things (IoT) System on a Chip (SoC) Development". Design And Reuse. Retrieved September 25, 2018.

- ^ "Is a single-chip SOC processor right for your embedded project?". Embedded. Retrieved October 13, 2018.

- ^ "Qualcomm launches SoCs for embedded vision | Imaging and Machine Vision Europe". www.imveurope.com. Retrieved October 13, 2018.

- ^ "Samsung Galaxy S10 and S10e Teardown". iFixit. March 6, 2019.

- ^ "ARM is going after Intel with new chip roadmap through 2020". Windows Central. Retrieved October 6, 2018.

- ^ "Always Connected PCs, Extended Battery Life 4G LTE Laptops | Windows". www.microsoft.com. Retrieved October 6, 2018.

- ^ "Gigabit Class LTE, 4G LTE and 5G Cellular Modems | Qualcomm". Qualcomm. Retrieved October 13, 2018.

- ^ OCLC 44267964.

- ^ OCLC 869378184.

- ^ OCLC 895661009.

- ^ "Best Practices for FPGA Prototyping of MATLAB and Simulink Algorithms". EEJournal. August 25, 2011. Retrieved October 8, 2018.

- ^ Bowyer, Bryan (February 5, 2005). "The 'why' and 'what' of algorithmic synthesis". EE Times. Retrieved October 8, 2018.

- ^ EE Times. "Is verification really 70 percent?." June 14, 2004. Retrieved July 28, 2015.

- ^ "Difference between Verification and Validation". Software Testing Class. August 26, 2013. Retrieved April 30, 2018.

In interviews most of the interviewers are asking questions on "What is Difference between Verification and Validation?" Many people use verification and validation interchangeably but both have different meanings.

- ^ Rittman, Danny (January 5, 2006). "Nanometer prototyping" (PDF). Tayden Design. Retrieved October 7, 2018.

- ^ "FPGA Prototyping to Structured ASIC Production to Reduce Cost, Risk & TTM". Design And Reuse. Retrieved October 7, 2018.

- ^ Brian Bailey, EE Times. "Tektronix hopes to shake up ASIC prototyping." October 30, 2012. Retrieved July 28, 2015.

- ^ OCLC 934678500.

- ISBN 978-1-4020-5352-8.

- ^ "FPGA vs ASIC: Differences between them and which one to use? – Numato Lab Help Center". numato.com. July 17, 2018. Retrieved October 17, 2018.

- ^ EE Times. "The Great Debate: SOC vs. SIP." March 21, 2005. Retrieved July 28, 2015.

- ^ "COSMIC". www.ece.ust.hk. Retrieved October 8, 2018.

Further reading

- Badawy, Wael; Jullien, Graham A., eds. (2003). System-on-Chip for Real-Time Applications. Kluwer international series in engineering and computer science, SECS 711. Boston: OCLC 50478525. 465 pages.

- Furber, Stephen B. (2000). ISBN 0-201-67519-6.

- Kundu, Santanu; Chattopadhyay, Santanu (2014). Network-on-chip: the Next Generation of System-on-Chip Integration (1st ed.). Boca Raton, FL: CRC Press. OCLC 895661009.

External links

- SOCC Annual IEEE International SoC Conference

- Baya free SoC platform assembly and IP integration tool

- Systems on Chip for Embedded Applications, VLSI

- Instant SoC SoC for FPGAs defined by C++

- MPSoC – Annual Conference on MPSoC

- Annual Symposium