Pentium (original)

x86-16, IA-32 | |

| Extensions | |

|---|---|

| Physical specifications | |

| Transistors | |

| Cores |

|

| Socket(s) | |

| Products, models, variants | |

| Core name(s) |

|

| Model(s) |

|

| History | |

| Predecessor(s) | i486 |

| Successor(s) | P6, Pentium II, Pentium III (SSE successor) |

| Support status | |

| Unsupported | |

The Pentium (also referred to as the i586) is a x86 microprocessor introduced by Intel on March 22, 1993. It is the first CPU using the Pentium brand.[2][3] Considered the fifth generation in the 8086 compatible line of processors,[4] its implementation and microarchitecture was internally called P5.

Like the Intel i486, the Pentium is instruction set compatible with the 32-bit i386. It uses a very similar microarchitecture to the i486, but was extended enough to implement a dual integer pipeline design, as well as a more advanced floating-point unit. The former is something that had been argued being impossible to implement for a CISC instruction set, by certain academics and RISC competitors.[who?]

The P5 Pentium is the first superscalar x86 processor, meaning it was often able to execute two instructions at the same time. Some techniques used to implement this were based on the earlier superscalar Intel i960 CA (1989), while other details were invented exclusively for the P5 design. Large parts were also copied from the i386 or i486, especially the strategies used to cope with the complicated x86 encodings in a pipelined fashion.[5] Just like the i486, the Pentium used both an optimized microcode system and RISC-like techniques, depending on the particular instruction, or part of instruction.

Other central features include a redesigned and significantly faster floating-point unit, a wide 64-bit

The P5 also has better support for multiprocessing compared to the i486, and is the first x86 CPU with hardware support for it similar to IBM mainframe computers. Intel worked with IBM to define this ability and also designed it into the P5 microarchitecture. This ability was absent in prior x86 generations and x86 processors from competitors.

In order to employ the dual pipelines at their full potential, certain compilers were optimized to better exploit instruction level parallelism, although not all applications would substatially gain from being recompiled. The faster FPU always enhanced floating point performance significantly though, compared to the i486 or i387. Intel spent resources working with development tool vendors, ISVs and operating system (OS) companies to optimize their products.

In October 1996, the similar Pentium MMX[6] was introduced, complementing the same basic microarchitecture with the MMX instruction set, larger caches, and some other enhancements.

Competitors included the superscalar

Intel discontinued the P5 Pentium processors (sold as a cheaper product since the release of the

Development

The P5 microarchitecture was designed by the same Santa Clara team which designed the 386 and 486.

Intel's

Intel used the Pentium name instead of 586, because in 1991, it had lost a trademark dispute over the "386" trademark, when a judge ruled that the number was generic. The company hired Lexicon Branding to come up with a new, non-numeric name.[18]

Improvements over the i486

The P5 microarchitecture brings several important advances over the prior i486 architecture.

- Performance:

- Superscalar architecture – The Pentium has two datapaths (pipelines) that allow it to complete two instructions per clock cycle in many cases. The main pipe (U) can handle any instruction, while the other (V) can handle the most common simple instructions. Some[who?] reduced instruction set computer (RISC) proponents had argued that the "complicated" x86 instruction set would probably never be implemented by a tightly pipelined microarchitecture, much less by a dual-pipeline design. The 486 and the Pentium demonstrated that this was indeed possible and feasible.

- data.

- Separation of code and data caches lessens the fetch and operand read/write conflicts compared to the 486. To reduce access time and implementation cost, both of them are 2-way associative, instead of the single 4-way cache of the 486. A related enhancement in the Pentium is the ability to read a contiguous block from the code cache even when it is split between two cache lines (at least 17 bytes in worst case).

- Much faster floating-point unit. Some instructions showed an enormous improvement, most notably FMUL, with up to 15 times higher throughput than in the 80486 FPU. The Pentium is also able to execute a FXCH ST(x) instruction in parallel with an ordinary (arithmetical or load/store) FPU instruction.

- Four-input address adders enables the Pentium to further reduce the address calculation latency compared to the 80486. The Pentium can calculate full addressing modes with segment-base + base-register + scaled register + immediate offset in a single cycle; the 486 has a three-input address adder only, and must therefore divide such calculations between two cycles.

- The 80486needed three clocks per iteration (and the earliest x86 chips significantly more than the 486). Also, optimization of the access to the first microcode words during the decode stages helps in making several frequent instructions execute significantly more quickly, especially in their most common forms and in typical cases. Some examples are (486→Pentium, in clock cycles): CALL (3→1), RET (5→2), shifts/rotates (2–3→1).

- A faster, fully hardware-based multiplier makes instructions such as MUL and IMUL several times faster (and more predictable) than in the 80486; the execution time is reduced from 13 to 42 clock cycles down to 10–11 for 32-bit operands.

- Virtualized interrupt to speed up virtual 8086 mode.

- Branch prediction

- Other features:

- Enhanced debug features with the introduction of the Processor-based debug port (see Pentium Processor Debugging in the Developers Manual, Vol 1).

- Enhanced self-test features like the L1 cache parity check (see Cache Structure in the Developers Manual, Vol 1).

- New instructions: CPUID, CMPXCHG8B, RDTSC, RDMSR, WRMSR, RSM.

- Test registers TR0–TR7 and MOV instructions for access to them were eliminated.

- The later Pentium MMX also added the SIMD) instruction set extension marketed for use in multimedia applications. MMX could not be used simultaneously with the x87FPU instructions because the registers were reused (to allow fast context switches). More important enhancements were the doubling of the instruction and data cache sizes and a few microarchitectural changes for better performance.

The Pentium was designed to execute over 100 million instructions per second (MIPS),[19] and the 75 MHz model was able to reach 126.5 MIPS in certain benchmarks.[20] The Pentium architecture typically offered just under twice the performance of a 486 processor per clock cycle in common benchmarks. The fastest 80486 parts (with slightly improved microarchitecture and 100 MHz operation) were almost as powerful as the first-generation Pentiums, and the AMD Am5x86, which despite its name is actually a 486-class CPU, was roughly equal to the Pentium 75 regarding pure ALU performance.

Errata

The early versions of 60–100 MHz P5 Pentiums had a problem in the floating-point unit that resulted in incorrect (but predictable) results from some division operations. This flaw, discovered in 1994 by professor Thomas Nicely at Lynchburg College, Virginia, became widely known as the Pentium FDIV bug and caused embarrassment for Intel, which created an exchange program to replace the faulty processors.

In 1997, another erratum was discovered that could allow a malicious program to crash a system without any special privileges, the "F00F bug". All P5 series processors were affected and no fixed steppings were ever released, however contemporary operating systems were patched with workarounds to prevent crashes.

Cores and steppings

The Pentium was Intel's primary microprocessor for personal computers during the mid-1990s. The original design was reimplemented in newer processes and new features were added to maintain its competitiveness, and to address specific markets such as portable computers. As a result, there were several variants of the P5 microarchitecture.

P5

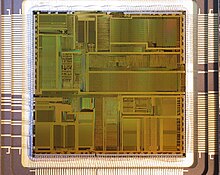

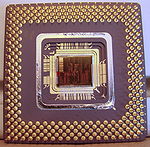

The first Pentium microprocessor core was code-named "P5". Its product code was 80501 (80500 for the earliest

P54C

The P5 was followed by the P54C (80502) in 1994, with versions specified to operate at 75, 90, or 100 MHz using a 3.3 volt power supply. Marking the switch to

P54CQS

The P54C was followed by the P54CQS in early 1995, which operated at 120 MHz. It was fabricated in a

P54CS

The P54CQS was quickly followed by the P54CS, which operated at 133, 150, 166 and 200 MHz, and introduced Socket 7. It contained 3.3 million transistors, measured 90 mm2 and was fabricated in a 350 nm BiCMOS process with four levels of interconnect.

P24T

The P24T

P55C

The P55C (or 80503) was developed by Intel's Research & Development Center in Haifa, Israel. It was sold as Pentium with MMX Technology (usually just called Pentium MMX); although it was based on the P5 core, it featured a new set of 57 "MMX" instructions intended to improve performance on multimedia tasks, such as encoding and decoding digital media data. The Pentium MMX line was introduced on October 22, 1996, and released in January 1997.[24]

The new instructions worked on new data types: 64-bit packed vectors of either eight 8-bit integers, four 16-bit integers, two 32-bit integers, or one 64-bit integer. So, for example, the PADDUSB (Packed ADD Unsigned Saturated Byte) instruction adds two vectors, each containing eight 8-bit unsigned integers together, elementwise; each addition that would

Other changes to the core include a 6-stage pipeline (vs. 5 on P5) with a return stack (first done on Cyrix 6x86) and better parallelism, an improved instruction decoder, 16KB L1 data cache + 16KB L1 instruction cache with Both 4-way associativity (vs. 8KB L1 Data/instruction with 2-way on P5), 4 write buffers that could now be used by either pipeline (vs. one corresponding to each pipeline on P5) and an improved branch predictor taken from the Pentium Pro,[25][26] with a 512-entry buffer (vs. 256 on P5).[27]

It contained 4.5 million transistors and had an area of 140 mm2. It was fabricated in a 280 nm CMOS process with the same metal pitches as the previous 350 nm BiCMOS process, so Intel described it as "350 nm" because of its similar transistor density.[28] The process has four levels of interconnect.[28]

While the P55C remained compatible with Socket 7, the voltage requirements for powering the chip differ from the standard Socket 7 specifications. Most motherboards manufactured for Socket 7 before the establishment of the P55C standard are not compliant with the dual voltage rail required for proper operation of this CPU (2.8 volt core voltage, 3.3 volt input/output (I/O) voltage). Intel addressed the issue with OverDrive upgrade kits that featured an interposer with its own voltage regulation.

Tillamook

Pentium MMX notebook CPUs used a mobile module that held the CPU. This module was a

Models and variants

|

|

|

|

| ||||||||||||||||||

| Code name | P5 | P54C | P54C/P54CQS | P54CS | P55C | Tillamook | ||||||||||||||||

| Product code | 80501 | 80502 | 80503 | |||||||||||||||||||

| Process size | 800 nm | 600 nm or 350 nm* | 350 nm | 350 nm (later 280 nm) | 250 nm | |||||||||||||||||

| Die area ( mm2 )

|

293.92 (16.7 x 17.6 mm) | 148 @ 600 nm / 91 (later 83) @ 350 nm | 91 (later 83) | 141 @ 350 nm / 128 @ 280 nm | 94.47 (9.06272 x 10.42416 mm) | |||||||||||||||||

| Number of transistors (millions) | 3.10 | 3.20 | 3.30 | 4.50 | ||||||||||||||||||

| Socket | Socket 4 | Socket 5/7 | Socket 7 | |||||||||||||||||||

| Package | CPGA /CPGA+IHS

|

CPGA/CPGA+IHS/ TCP *

|

CPGA/TCP* | CPGA/TCP* | CPGA/PPGA | PPGA | TCP* | CPGA/PPGA/TCP* | PPGA/TCP* | TCP/TCP on MMC-1 | ||||||||||||

| Clock speed ( MHz )

|

60 | 66 | 75 | 90 | 100 | 120 | 133 | 150 | 166 | 200 | 120* | 133* | 150* | 166 | 200 | 233 | 166 | 200 | 233 | 266 | 300 | |

| Bus speed ( MHz )

|

60 | 66 | 50 | 60 | 50 | 66 | 60 | 66 | 60 | 66 | 60 | 66 | 60 | 66 | ||||||||

| Level 1 Cache Size | 8 KB 2-way set associative code cache. 8 KB 2-way set associative write-back data cache | 16 KB 4-way set associative code cache. 16 KB 4-way set associative write-back data cache | ||||||||||||||||||||

| Core Voltage | 5.0 | 5.15 | 3.3 2,9* | 3.3 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 3.1* 2.9* | 3.3 | 3.3 | 2.2* | 2.45* | 2.45* | 2.8 2.45* | 2.8 | 2.8 | 1.9 1.8* | 1.8* | 1.8* | 1.9 2.0* | 2.0* | |

| I/O Voltage | 5.0 | 5.15 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 2.5 | 2.5 | 2.5 | 2.5 | 2.5 | |

| TDP (max. W) | 14.6 (15.3) | 16.0 (17.3) | 8.0 (9.5) 6.0* (7.3*) | 9.0 (10.6) 7.3* (8.8*) | 10.1 (11.7) 8.0 at 600nm* (9.8 at 600nm*) 5.9 at 35Onm* (7.6 at 350nm*) | 12.8 (13.4) 7.1* (8.8*) | 11.2 (12.2) 7.9* (9.8*) | 11.6 (13.9) 10.0* (12.0*) | 14.5 (15.3) | 15.5 (16.6) | 4.2* | 7.8* (11.8*) | 8.6* (12.7*) | 13.1 (15.7) 9.0* (13.7*) | 15.7 (18.9) | 17.0 (21.5) | 4.5 (7.4) 4.1* (5.4*) | 5.0* (6.1*) | 5.5* (7.0*) | 7.6 (9.2) 7.6* (9.6*) | 8.0* | |

| Introduced | 1993-03-22 | 1994-10-10 | 1994-03-07 | 1995-03-27 | 1995-06-12 | 1996-01-04 | 1996-06-10 | 1996-10-20 | 1997-05-19 | 1997-01-08 | 1997-06-02 | 1997-08 | 1998-01 | 1999-01 | ||||||||

| * An asterisk indicates that these were only available as Mobile Pentium or Mobile Pentium MMX chips for laptops. | ||||||||||||||||||||||

| |||||||

| Code name | P54CTB | ||||||

| Product code | PODPMT60X150 | PODPMT66X166 | PODPMT60X180 | PODPMT66X200 | |||

| Process size (nm) | 350 | ||||||

| Socket | Socket 5/7 | ||||||

| Package | CPGA with heatsink, fan and voltage regulator

| ||||||

| Clock speed (MHz) | 125 | 150 | 166 | 150 | 180 | 200 | |

| Bus speed (MHz) | 50 | 60 | 66 | 50 | 60 | 66 | |

| Upgrade for | Pentium 75 | Pentium 90 | Pentium 100 and 133 | Pentium 75 | Pentium 90, 120 and 150 | Pentium 100, 133 and 166 | |

| TDP (max. W) | 15.6 | 15.6 | 15.6 | 18 | |||

| Voltage | 3.3 | 3.3 | 3.3 | 3.3 | |||

|

| ||||||

| Code name | P55C | Tillamook | |||||

| Product code | FV8050366200 | FV8050366233 | FV80503CSM66166 | GC80503CSM66166 | GC80503CS166EXT | FV80503CSM66266 | GC80503CSM66266 |

| Process size ( nm )

|

350 | 250 | |||||

| Clock speed ( MHz )

|

200 | 233 | 166 | 166 | 166 | 266 | 266 |

| Bus speed ( MHz )

|

66 | 66 | 66 | 66 | 66 | 66 | 66 |

| Package | PPGA | PPGA | PPGA | BGA | BGA | PPGA | BGA |

| TDP (max. W) | 15.7 | 17 | 4.5 | 4.1 | 4.1 | 7.6 | 7.6 |

| Voltage | 2.8 | 2.8 | 1.9 | 1.8 | 1.8 | 1.9 | 2.0 |

Competitors

After the introduction of the Pentium, competitors such as

List

- AMD K5, AMD K6

- Cyrix 6x86

- WinChip C6

- NexGen Nx586

- Rise mP6

See also

- List of Intel CPU microarchitectures

- List of Intel Pentium processors

- Cache on a stick (COASt), L2 cache modules for Pentium

- IA-32 instruction set architecture (ISA)

- Intel 82497 cache controller

References

- ^ a b "Product Change Notification #777" (PDF). Intel. February 9, 1999. Archived from the original (PDF) on January 27, 2000. Retrieved October 14, 2019.

- ^ View Processors Chronologically by Date of Introduction, Intel, retrieved August 14, 2007

- ^ Intel Pentium Processor Family, Intel, retrieved August 14, 2007

- ^ I.e. 8086/88, 186/286, 386, 486, P5

- ^ as compared to a simple RISC processor like the i960.

- ^ officially known as Pentium with MMX Technology

- ISBN 978-0-471-73617-2.

- ^ Business Week. No. 3268. June 1, 1992.

- ^ House, Dave, "Putting the RISC vs. CISC Debate to Rest", Intel Corporation, Microcomputer Solutions, November/December 1991, page 18

- ^ Horten, Monica (May 1, 1993). "The hot new star of microchips". New Scientist. No. 1871. pp. 31 ff. Archived from the original on July 27, 2011. Retrieved June 9, 2009.

- ^ Quinlan, Tom (March 16, 1992). "Intel to offer a peek at its '586' chip". InfoWorld. p. 8.

- ^ Quinlan, Tom; Corcoran, Cate (June 15, 1992). "Design woes force Intel to cancel 586 chip demo". InfoWorld. Vol. 14, no. 24. p. 1.

- ^ Quinlan, Tom; Corcoran, Cate (July 27, 1992). "P5 chip delay won't alter rivals' plans". InfoWorld. Vol. 14, no. 30. pp. 1, 103.

- ISSN 0199-6649.

- .

- S2CID 52799248. Retrieved August 18, 2023.

- ^ Shimpi, Anand Lal (January 27, 2010), Why Pine Trail Isn't Much Faster Than the First Atom, retrieved August 4, 2010

- ^ Smith, Ernie (June 14, 2017). "Why Intel Couldn't Trademark Numbers Anymore". Vice. Retrieved July 13, 2023.

- ^ "PC users guide: General Computer Information". Archived from the original on July 28, 2007. Retrieved September 14, 2007.

- ^ Polsson, Ken. "Chronology of Microprocessors".

- ^ Case, Brian (March 29, 1993). "Intel Reveals Pentium Implementation Details". Microprocessor Report.

- ^ "Intel Pentium processor (510\60, 567\66). Nov 1994" (PDF).

- ^ a b c d Gwennap, Linley (March 27, 1995). "Pentium is First CPU to Reach 0.35 Micron". Microprocessor Report.

- ^ New Chip Begs New Questions, CNet, retrieved February 6, 2009

- ^ "Intel Architecture Optimization Manual" (PDF). 1997. pp. 2–16. Archived from the original (PDF) on July 5, 2017. Retrieved September 1, 2017.

- ^ "Phil Storrs PC Hardware book". Archived from the original on January 20, 2020. Retrieved September 1, 2017.

- ^ "Pentium Processor with MMX Technology" (PDF). 1997. Archived from the original (PDF) on July 5, 2010. Retrieved September 1, 2017.

- ^ a b Slater, Michael (March 5, 1996). "Intel's Long-Awaited P55C Disclosed". Microprocessor Report.

- ^ Corcoran, Cate; Crothers, Brooke (July 11, 1994). "NexGen to Beat Intel's Chip Prices". InfoWorld. IDG: 5.

- PC Magazine. 13 (1). Ziff Davis: 29.

- CIO magazine. 8 (17). IDG: 72–76.

- PC Magazine. 16 (16). Ziff Davis: 130–133.

External links

- CPU-Collection.de - Intel Pentium images and descriptions

- Plasma Online Intel CPU Identification

- The Pentium Timeline Project Archived December 23, 2021, at the Wayback Machine The Pentium Timeline Project maps oldest and youngest chip known of every s-spec made. Data are shown in an interactive timeline.

Intel datasheets

- Pentium (P5)

- Pentium (P54)

- Pentium MMX (P55C)

- Mobile Pentium MMX (P55C)

- Mobile Pentium MMX (Tillamook)

Intel manuals

These official manuals provide an overview of the Pentium processor and its features:

- Pentium Processor Family Developer's Manual Pentium Processor (Volume 1) (Intel order number 241428)

- Pentium Processor Family Developer's Manual Volume 2: Instruction Set Reference Archived March 13, 2012, at the Wayback Machine (Intel order number 243191)

- Pentium Processor Family Developer's Manual Volume 3: Architecture and Programming Manual[permanent dead link] (Intel order number 241430)