NAND logic

The mathematical proof for this was published by Henry M. Sheffer in 1913 in the Transactions of the American Mathematical Society (Sheffer 1913). A similar case applies to the NOR function, and this is referred to as NOR logic.

NAND

A NAND gate is an inverted AND gate. It has the following truth table:

| ||||||||||||||||

|

Q = A NAND B

| ||||||||||||||||

In

Making other gates by using NAND gates

A NAND gate is a

NOT

A NOT gate is made by joining the inputs of a NAND gate together. Since a NAND gate is equivalent to an AND gate followed by a NOT gate, joining the inputs of a NAND gate leaves only the NOT gate.

| Desired NOT Gate | NAND Construction | ||||||

|---|---|---|---|---|---|---|---|

|

| ||||||

| Q = NOT( A ) | = A NAND A | ||||||

| |||||||

AND

An AND gate is made by inverting the output of a NAND gate as shown below.

| Desired AND Gate | NAND Construction | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||||||||

| Q = A AND B | = ( A NAND B ) NAND ( A NAND B ) | |||||||||||||||

| ||||||||||||||||

OR

If the truth table for a NAND gate is examined or by applying

| Desired OR Gate | NAND Construction | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||||||||

| Q = A OR B | = ( A NAND A ) NAND ( B NAND B ) | |||||||||||||||

| ||||||||||||||||

NOR

A NOR gate is an OR gate with an inverted output. Output is high when neither input A nor input B is high.

| Desired NOR Gate | NAND Construction | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||||||||

| Q = A NOR B | = [ ( A NAND A ) NAND ( B NAND B ) ] NAND [ ( A NAND A ) NAND ( B NAND B ) ] | |||||||||||||||

| ||||||||||||||||

XOR

An XOR gate is made by connecting four NAND gates as shown below. This construction entails a propagation delay three times that of a single NAND gate.

| Desired XOR Gate | NAND Construction | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||||||||

| Q = A XOR B | = [ A NAND ( A NAND B ) ] NAND [ B NAND ( A NAND B ) ] | |||||||||||||||

| ||||||||||||||||

Alternatively, an XOR gate is made by considering the disjunctive normal form , noting from

| Desired Gate | NAND Construction |

|---|---|

|

|

| Q = A XOR B | = [ B NAND ( A NAND A ) ] NAND [ A NAND ( B NAND B ) ] |

XNOR

An XNOR gate is made by considering the disjunctive normal form , noting from

| Desired XNOR Gate | NAND Construction | |||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| |||||||||||||||

| Q = A XNOR B | = [ ( A NAND A ) NAND ( B NAND B ) ] NAND ( A NAND B ) | |||||||||||||||

| ||||||||||||||||

Alternatively, the 4-gate version of the XOR gate can be used with an inverter. This construction has a propagation delay four times (instead of three times) that of a single NAND gate.

| Desired Gate | NAND Construction |

|---|---|

|

|

| Q = A XNOR B | = { [ A NAND ( A NAND B ) ] NAND [ B NAND ( A NAND B ) ] } NAND { [ A NAND ( A NAND B ) ] NAND [ B NAND ( A NAND B ) ] } |

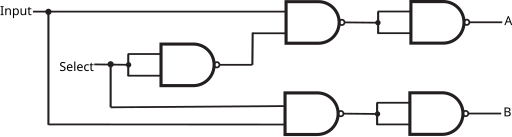

MUX

A multiplexer or a MUX gate is a three-input gate that uses one of the inputs, called the selector bit, to select one of the other two inputs, called data bits, and outputs only the selected data bit.[1]

DEMUX

A demultiplexer performs the opposite function of a multiplexer: It takes a single input and channels it to one of two possible outputs according to a selector bit that specifies which output to choose.[1][copyright violation?]

| Desired DEMUX Gate | NAND Construction | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||

See also

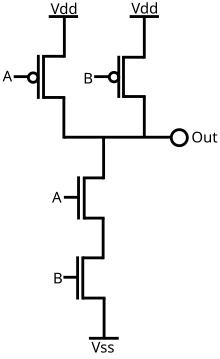

- CMOS transistor structures and chip deposition geometries that produce NAND logic elements

- Sheffer stroke – other name

- NOR logic. Like NAND gates, NOR gates are also universal gates.

- Functional completeness

References

- ^ a b Nisan, Noam; Schocken, Shimon (2005). "1. Boolean Logic". From NAND to Tetris: Building a Modern Computer from First Principles (PDF). The MIT Press. Archived from the original (PDF) on 2017-01-10.

- ISBN 0-672-21035-5.

- Sheffer, H. M. (1913), "A set of five independent postulates for Boolean algebras, with application to logical constants", Transactions of the American Mathematical Society, 14 (4): 481–488, JSTOR 1988701

External links

- TTL NAND and AND gates - All About Circuits

- Steps to Derive XOR from NAND gate.

- NandGame - a game about building a computer using only NAND gates