NOR gate

This article needs additional citations for verification. (September 2016) |

| NOR gate truth table | ||

|---|---|---|

| Input | Output | |

| A | B | A NOR B |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

The NOR gate is a digital

In most, but not all, circuit implementations, the negation comes for free—including CMOS and TTL. In such logic families, OR is the more complicated operation; it may use a NOR followed by a NOT. A significant exception is some forms of the domino logic family.

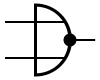

Symbols

There are three symbols for NOR gates: the American (ANSI or 'military') symbol and the IEC ('European' or 'rectangular') symbol, as well as the deprecated

|

|

|

| MIL/ANSI Symbol | IEC Symbol | DIN Symbol |

Hardware description and pinout

NOR Gates are basic logic gates, and as such they are recognised in

|

1 Input A1 2 Input B1 3 Output Q1 4 Output Q2 5 Input B2 6 Input A2 7 Vss 8 Input A3 9 Input B3 10 Output Q3 11 Output Q4 12 Input B4 13 Input A4 14 Vdd |

Availability

These devices are available from most semiconductor manufacturers such as

In the popular CMOS and TTL

- CMOS

- 4001: Quad 2-input NOR gate

- 4025: Triple 3-input NOR gate

- 4002: Dual 4-input NOR gate

- 4078: Single 8-input NOR gate

- TTL

- 7402: Quad 2-input NOR gate

- 7427: Triple 3-input NOR gate

- 7425: Dual 4-input NOR gate (with strobe, obsolete)

- 74260: Dual 5-Input NOR Gate

- 744078: Single 8-input NOR Gate

In the older RTL and ECL families, NOR gates were efficient and most commonly used.

Implementations

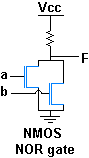

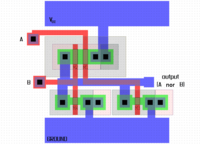

|

|

The diagrams above show the construction of a 2-input NOR gate using NMOS logic circuitry. If either of the inputs is high, the corresponding N-channel MOSFET is turned on and the output is pulled low; otherwise the output is pulled high through the pull-up resistor.

The diagram below shows a 2-input NOR gate using CMOS technology. The diodes and resistors on the inputs are to protect the CMOS components from damage due to electrostatic discharge (ESD) and play no part in the logical function of the circuit.

Functional completeness

The NOR gate has the property of functional completeness, which it shares with the NAND gate. That is, any other logic function (AND, OR, etc.) can be implemented using only NOR gates.[1] An entire processor can be created using NOR gates alone. The original Apollo Guidance Computer used 4,100 integrated circuits (IC), each one containing only two 3-input NOR gates.[2]

As NAND gates are also functionally complete, if no specific NOR gates are available, one can be made from NAND gates using NAND logic.[1]

| Desired gate | NAND Construction |

|---|---|

|

|

See also

- AND gate

- OR gate

- NOT gate

- NAND gate

- XOR gate

- XNOR gate

- NAND logic

- Boolean algebra (logic)

- Flash memory

References

- ^ a b Mano, M. Morris and Charles R. Kime. Logic and Computer Design Fundamentals, Third Edition. Prentice Hall, 2004. p. 73.

- ^ Whipple, Walt (2019). First-Hand:Hacking Apollo's Guidance Computer. Engineering and Technology History Wiki.