AMD 10h

This article needs to be updated. (October 2010) |

| General information | |

|---|---|

| Launched | 2007 |

| Discontinued | 2012 |

| Common manufacturer(s) |

|

| History | |

| Predecessor(s) | K8 - Hammer |

| Successor(s) | Bulldozer - Family 15h |

| Support status | |

| iGPU unsupported | |

The AMD Family 10h, or K10, is a

Nomenclature

It appears that AMD has not used K-nomenclature (which originally stood for "Kryptonite" in the K5 processor[2]) from the time after the use of the codename K8 for the AMD K8 or Athlon 64 processor family, since no K-nomenclature naming convention beyond K8 has appeared in official AMD documents and press releases after the beginning of 2005.

The name "K8L" was first coined by Charlie Demerjian in 2005, at the time a writer at The Inquirer,[3] and was used by the wider IT community as a convenient shorthand[4] while according to AMD official documents, the processor family was termed "AMD Next Generation Processor Technology".[5]

The microarchitecture has also been referred to as Stars, as the codenames for desktop line of processors was named under stars or constellations (the initial Phenom models being codenamed Agena and

In a video interview,[6] Giuseppe Amato confirmed that the codename is K10.

It was revealed, by The Inquirer itself, that the codename "K8L" referred to a low-power version of the K8 family, later named

AMD refers to it as Family 10h Processors, as it is the successor of the Family 0Fh Processors (codename K8). 10h and 0Fh refer to the main result of the CPUID x86 processor instruction. In hexadecimal numbering, 0Fh (h represents hexadecimal numbering) equals the decimal number 15, and 10h equals decimal 16. (The "K10h" form that sometimes pops up is an improper hybrid of the "K" code and Family identifier number.)

Schedule of launch and delivery

Timeline

Historical information

In 2003, AMD outlined the features for upcoming generations of microprocessors after the K8 family of processors in various events and analyst meetings, including the Microprocessor Forum 2003.[7] The outlined features to be deployed by the next-generation microprocessors are as follows:

- Threaded architectures.

- Chip level multiprocessing.

- Huge scale MP (multi-processor) machines.

- 10 GHz operation.

- Much higher performance superscalar, out-of-orderCPU core.

- Huge caches.

- Media/vector processingextensions.

- Branch and memory hints.

- Security and virtualization.

- Enhanced Branch Predictors.

- Static and dynamic power management.

In June 2006, AMD executive vice president Henri Richard had an interview with DigiTimes commented on the upcoming processor developments:

Q: What is your broad perspective on the development of AMD processor technology over the next three to four years?

A: Well, as Dirk Meyer commented at our analysts meeting, we're not standing still. We've talked about the refresh of the current K8 architecture that will come in '07, with significant improvements in many different areas of the processor, including integer performance, floating point performance, memory bandwidth, interconnections and so on.

— AMD Executive Vice President, Henri Richard, Source: DigiTimes Interview with Henri Richard[8]

Live demonstrations

On November 30, 2006, AMD live demonstrated the native quad core chip known as "Barcelona" for the first time in public,[9] while running Windows Server 2003 64-bit Edition. AMD claims 70% scaling of performance in real world loads, and better performance than Intel Xeon 5355 processor codenamed Clovertown.[10]

On January 24, 2007, AMD Executive Vice President Randy Allen claimed that in live tests, in regard to a wide variety of workloads, "Barcelona" was able to demonstrate 40% performance advantage over the comparable Intel Xeon codenamed

On May 10, 2007, AMD held a private event demonstrating the upcoming processors codenamed Agena FX and chipsets, with one demonstrated system being

Sister microarchitecture

On the December 2006 analyst day, Executive vice president Marty Seyer announced a new mobile core codenamed

TLB bug

In November 2007 AMD stopped delivery of Barcelona processors after a

Features

Fabrication technology

AMD has introduced the microprocessors manufactured at

Supported DRAM standards

The

While some desktop K10 processors are AM2+ supporting only DDR2, an AM3 K10 processor supports both DDR2 and DDR3. A few AM3 motherboards have both DDR2 and DDR3 slots (this does not mean that both types can be fitted at the same time), but for the most part they have only DDR3.

Lynx desktop processors only support DDR3, as they use the FM1 socket.

Microarchitecture characteristics

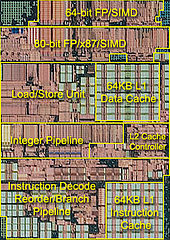

Characteristics of the microarchitecture include the following:[18]

- Form factors

- Socket AM2+ with DDR2 for the 65 nm Phenom and Athlon 7000 Series

- DDR3 for Semprons and the 45 nm Phenom II and Athlon II Series. They can also be used on AM3+ motherboards with DDR3. Note that, while all K10 Phenom Processors are backwards compatible with Socket AM2+ and Socket AM2, some 45 nm Phenom II Processors are only available for Socket AM2+. Lynx processors do not use either AM2+ nor AM3.

- Socket FM1 with DDR3 for Lynx processors.

- Socket F with DDR2, DDR3 with Shanghai and later Opteron processors

- Instruction set additions and extensions

- New bit-manipulation ABM: Leading Zero Count (LZCNT) and Population Count (POPCNT)

- New SSE instructions named as SSE4a: combined mask-shift instructions (EXTRQ/INSERTQ) and scalar streaming store instructions (MOVNTSD/MOVNTSS). These instructions are not found in Intel's SSE4

- Support for unaligned SSE load-operation instructions (which formerly required 16-byte alignment)[19]

- New bit-manipulation

- Execution pipeline enhancements

- 128-bit wide SSE units

- Wider L1 data cache interface allowing for two 128-bit loads per cycle (as opposed to two 64-bit loads per cycle with K8)

- Lower integer divide latency

- 512-entry indirect branch predictor and a larger return stack (size doubled from K8) and branch target buffer

- Side-Band Stack Optimizer, dedicated to perform increment/decrement of register stack pointer

- Fastpathed CALL and RET-Imm instructions (formerly microcoded) as well as MOVs from SIMD registers to general purpose registers

- Integration of new technologies onto CPU die:

- Four processor cores (Quad-core)

- Split power planes for CPU core and memory controller/northbridge for more effective power management, first dubbed Dynamic Independent Core Engagement or D. I. C. E. by AMD and now known as Enhanced PowerNow! (also dubbed Independent Dynamic Core Technology), allowing the cores and northbridge (integrated memory controller) to scale power consumption up or down independently.[20]

- Shutting down portions of the circuits in core when not in load, named "CoolCore" Technology.

- Improvements in the memory subsystem:

- Improvements in access latency:

- Support for re-ordering loads ahead of other loads and stores

- More aggressive instruction prefetching, 32 bytes instruction prefetch as opposed to 16 bytes in K8

- DRAM prefetcher for buffering reads

- Buffered burst writeback to RAM in order to reduce contention

- Changes in memory hierarchy:

- Prefetch directly into L1 cache as opposed to L2 cache with K8 family

- 32-way set associative L3 victim cache sized at least 2 MB, shared between processing cores on a single die (each with 512 K of independent exclusive L2 cache), with a sharing-aware replacement policy.

- Extensible L3 cache design, with 6 MB planned for 45 nmprocess node, with the chips codenamed Shanghai.

- Changes in address space management:

- Two 64-bit independent memory controllers, each with its own physical address space; this provides an opportunity to better utilize the available bandwidth in case of random memory accesses occurring in heavily multi-threaded environments. This approach is in contrast to the previous "interleaved" design, where the two 64-bit data channels were bounded to a single common address space.

- Larger Tagged Lookaside Buffers; support for 1 GB page entries and a new 128-entry 2 MB page TLB

- 48-bit memory addressing to allow for 256 TB memory subsystems[21]

- Memory mirroring (alternatively mapped DIMM addressing),RAS

- AMD-V Nested Pagingfor improved MMU virtualization, claimed to have decreasing world switch time by 25%.

- Improvements in access latency:

- Improvements in system interconnect:

- HyperTransport retry support

- Support for HyperTransport 3.0, with HyperTransport Link unganging which creates 8 point-to-point links per socket.

- Platform-level enhancements with additional functionality:

- Five p-states allowing for automatic clock rate modulation

- Increased clock gating

- Official support for coprocessors via HTX slots and vacant CPU sockets through HyperTransport: Torrenza initiative.

Feature tables

CPUs

This section is empty. You can help by adding to it. (March 2023) |

APUs

Desktop

Phenom models

Agena (65 nm SOI, quad-core)

- Four AMD K10 cores

- L1 cache: 64 KB instructions) per core

- L2 cache: 512 KB per core, full-speed

- L3 cache: 2 MB shared between all cores

- Memory controller: dual channel DDR2-1066 MHz with unganging option

- AMD-V

- Socket AM2+, HyperTransport with 1600 to 2000 MHz

- Power consumption (TDP): 65, 95, 125 and 140 Watt

- First release

- November 19, 2007 (B2 Stepping)

- March 27, 2008 (B3 Stepping)

- Clock rate: 1800 to 2600 MHz

- Models: Phenom X4 9100e - 9950

Toliman (65 nm SOI, tri-core)

- Three AMD K10 cores

- L1 cache: 64 KB instruction and 64 KB data cache per core

- L2 cache: 512 KB per core, full-speed

- L3 cache: 2 MB shared between all cores

- Memory controller: dual channel DDR2-1066 MHz with unganging option

- AMD-V

- Socket AM2+, HyperTransport with 1600 to 1800 MHz

- Power consumption (TDP): 65 and 95 Watt

- First release

- March 27, 2008 (B2 Stepping)

- April 23, 2008 (B3 Stepping)

- Clock rate: 2100 to 2500 MHz

- Models: Phenom X3 8250e - 8850

Phenom II models

Thuban (45 nm SOI, hexa-core)

- Six AMD K10 cores

- L1 cache: 64 KB instructions and 64 KB data per core

- L2 cache: 512 KB per core, full-speed

- L3 cache: 6 MB shared between all cores.

- Memory controller: dual channel DDR2-1066 MHz (AM2+), dual channel DDR3-1333 (AM3) with unganging option

- AMD-V

- Socket AM2+, Socket AM3, HyperTransport with 1800 to 2000 MHz

- Power consumption (TDP): 95 or 125 Watt

- First release

- 27 April 2010 (E0 Stepping)

- Clock rate: 2.6 - 3.3 GHz; up to 3.7 GHz with Turbo Core

- Models: Phenom II X6 1035T, 1045T, 1055T, 1065T, 1075T, 1090T and 1100T

Zosma (45 nm SOI, quad-core)

- Four AMD K10 cores harvested from Thuban with two cores disabled[24]

- Turbo Core (AMD equivalent of Intel Turbo Boost)

- Memory support: DDR2 SDRAM up to PC2-8500, DDR3 SDRAM up to PC3-10600 (Socket AM3 only)

- Models: Phenom II X4 650T, 840T, 960T, 970(Thuban-based Zosma core, OEM Only, 970 has unlocked multiplier but w/o Turbo Core)

Deneb (45 nm SOI, quad-core)

- Four AMD K10 cores

- L1 cache: 64 KB instructions and 64 KB data per core

- L2 cache: 512 KB per core, full-speed

- L3 cache: 6 MB shared between all cores. The 800 series have 2 MB of its L3 Cache disabled due to defects.

- Memory controller: dual channel DDR2-1066 MHz (AM2+), dual channel DDR3-1333 (AM3) with unganging option

- AMD-V

- Socket AM2+, Socket AM3, HyperTransport with 1800 to 2000 MHz

- Power consumption (TDP): 65, 95, 125 and 140 Watt

- First release

- 8 January 2009 (C2 Stepping)

- Clock rate: 2500 to 3700 MHz

- Models: Phenom II X4 805 - 980 (except 840 and 850)

42 TWKR Limited Edition (45 nm SOI, quad-core)

AMD released a limited edition Deneb-based processor to extreme overclockers and partners. Fewer than 100 were manufactured.

The "42" officially represents four cores running at 2 GHz, but is also a reference to

- Four AMD K10 cores

- Models: Phenom II 42 TWKR

Propus (45 nm SOI, quad-core)

- Four AMD K10 cores harvested from Deneb with L3 cache disabled[24]

- AMD-V

- Memory support: DDR2 SDRAM up to PC2-8500 (DDR2-1066 MHz), DDR3 SDRAM up to PC3-10600 (DDR3-1333 MHz) (Socket AM3 only)

- Models: Phenom II X4 840 and 850

Heka (45 nm SOI, tri-core)

- Three AMD K10 cores using chip harvesting technique, with one core disabled

- L1 cache: 64 KB instructions and 64 KB data per core

- L2 cache: 512 KB per core, full-speed

- L3 cache: 6 MB shared between all cores

- Memory controller: dual channel DDR2-1066 MHz (AM2+), dual channel DDR3-1333 (AM3) with unganging option

- AMD-V

- Socket AM3, HyperTransport with 2000 MHz

- Power consumption (TDP): 65 and 95 Watt

- First release

- 9 February 2009 (C2 Stepping)

- Clock rate: 2500 to 3000 MHz

- Models: Phenom II X3 705e - 740

Callisto (45 nm SOI, dual-core)

- Two AMD K10 cores using chip harvesting technique, with two cores disabled

- L1 cache: 64 KB instructions and 64 KB data per core

- L2 cache: 512 KB per core, full-speed

- L3 cache: 6 MB shared between all cores

- Memory controller: dual channel DDR2-1066 MHz (AM2+), dual channel DDR3-1333 (AM3) with unganging option

- AMD-V

- Socket AM3, HyperTransport with 2000 MHz

- Power consumption (TDP): 80 Watt

- First release

- 1 June 2009 (C2 Stepping)

- Clock rate: 3000 to 3500 MHz

- Models: Phenom II X2 545 - 570

Regor (45 nm SOI, dual-core)

- Two AMD K10 cores

- Some are chip harvests from Propus or Deneb with two cores disabled[24]

- Most Regor-based processors feature double the L2 cache per core (1 MB) as other Athlon II and Phenom II processors.

- AMD64, Cool'n'Quiet, AMD-V

- Memory support: DDR2 SDRAM up to PC2-8500, DDR3 SDRAM up to PC3-8500 (DDR3-1066 MHz) (Socket AM3 only)

- Models: Phenom II X2 511 and 521

Athlon X2 models

Kuma (65 nm SOI, dual-core)

- Two AMD K10 cores harvested from Agena with two cores disabled[24]

- AMD-V[26]

- Models: Athlon X2 6500 - 7850

Regor/Deneb (45 nm SOI, dual-core)

- Two AMD K10 cores. Some 5000 series processors are chip harvests from Propus or Deneb; All 5200 series chips are harvests, each has two cores disabled[24]

- AMD-V[26]

- Models: Athlon X2 5000+ and 5200+

Athlon II Models

Zosma (45 nm SOI, quad-core)

- Four AMD K10 cores harvested from Thuban with two cores disabled[24]

- Turbo Core (AMD equivalent of Intel Turbo Boost)

- Memory support: DDR2 SDRAM up to PC2-8500, DDR3 SDRAM up to PC3-10600 (Socket AM3 only)

- Models: Athlon II X4 640[T]

Propus (45 nm SOI, quad-core)

- Four AMD K10 cores[27][28]

- L1 cache: 64 KB instructions and 64 KB data per core

- L2 cache: 512 KB per core, full-speed

- Memory controller: dual channel DDR2-1066 MHz (AM2+), dual channel DDR3-1333 (AM3) with unganging option

- AMD-V

- Socket AM3, HyperTransport with 2000 MHz

- Power consumption (TDP): 45 Watt or 95 Watt

- First release

- September 2009 (C2 Stepping)

- Clock rate: 2200 - 3100 MHz

- Models: Athlon II X4 600e - 650

Rana (45 nm SOI, tri-core)

- Three AMD K10 cores chip harvested from Propus or Deneb with one core disabled[24]

- L1 instructions) per core

- L2 cache: 512 kB per core, full-speed

- Memory controller: dual channel DDR2-1066 MHz (AM2+), dual channel DDR3-1333 (AM3) with unganging option

- AMD-V

- Socket AM3, HyperTransport with 2 GHz

- Die Size: 169 mm²[29]

- Power consumption (TDP): 45 Watts or 95 Watts

- First release

- October 2009 (Stepping C2)

- Clock rate: 2.2–3.4 GHz

- Models: Athlon II X3 400e - 460

Regor (45 nm SOI, dual-core)

- Two AMD K10 cores

- L1 cache: 64 KB instructions and 64 KB data per core

- L2 cache: 1024 KB per core, full-speed

- Memory controller: dual channel DDR2-1066 MHz (AM2+), dual channel DDR3-1333 (AM3) with unganging option

- AMD-V

- Socket AM3, HyperTransport with 2000 MHz

- Power consumption (TDP): 65 Watt

- First release

- June 2009 (C2 Stepping)

- Clock rate: 1600 - 3600 MHz

- Models: Athlon II X2 250u - 280

Sargas (45 nm SOI, single-core)

- Single AMD K10 core harvest from Regor with one core disabled[24]

- AMD-V

- Memory support: DDR2 SDRAM up to PC2-6400, DDR3 SDRAM up to PC3-8500 (Socket AM3 only)

- Models: Athlon II 160u and 170u

Lynx (32 nm SOI, dual or quad-core)

- Two or four AMD K10 cores with no L3 cache

- APUs without graphics. See below.

- Models: Athlon II X2 221 to Athlon II X4 651K

Sempron models

Sargas (45 nm SOI, single-core)

- Single AMD K10 core chip harvested from Regor with one core disabled[24]

- AMD-V

- Models: Sempron 130-150

Sempron X2 models

Regor (45 nm SOI, dual-core)

- Two AMD K10 cores

- AMD-V

- Models: Sempron X2 180 and 190

Lynx (32 nm SOI, dual-core)

- Two AMD K10 cores with no L3 cache

- APUs without graphics. See below.

- Models: Sempron X2 198

Llano "APUs"

Lynx (32 nm SOI, dual or quad-core)

The first generation desktop APUs based on the K10 microarchitecture were released in 2011 (some models do not provide graphics capability, such as the Lynx Athlon II and Sempron X2).

- Fabrication 32 nm on GlobalFoundries SOI process

- Socket FM1

- Die size: 228 mm2, with 1.178 billion transistors[30][31]

- AMD K10 cores with no L3 cache

- GPU: TeraScale 2

- All A and E series models feature Redwood-class integrated graphics on die (BeaverCreek for the dual-core variants and WinterPark for the quad-core variants). Sempron and Athlon models exclude integrated graphics.[32]

- Support for up to four DDR3-1866 memory

- 5 GT/s UMI

- Integrated PCIe 2.0controller

- Select models support Turbo Core technology for faster CPU operation when the thermal specification permits

- Select models support Hybrid Graphics technology to assist a discrete Radeon HD 6450, 6570, or 6670 discrete graphics card. This is similar to the current Hybrid CrossFireX technology available in the AMD 700 and 800 chipset series

- AMD-V

- Models: Lynx desktop APUs and CPUs

Mobile

Turion II (Ultra) models

"Caspian" (45nm SOI, dual-core)

- Tigris platform[33]

- Two AMD K10 cores

- AMD-V, PowerNow!

- Memory support: DDR2 SDRAM (Up to 800 MHz)

- Models: Turion II Ultra M600 to M660

Turion II models

"Caspian" (45nm SOI, dual-core)

- Tigris platform

- Two AMD K10 cores

- AMD-V, PowerNow!

- Memory support: DDR2 SDRAM (Up to 800 MHz)

- Models: Turion II M500 TO M560

"Champlain" (45nm SOI, dual-core)

- Danube platform[34][35]

- Two AMD K10 cores

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1333 MHz)

- Models: Turion II models

Athlon II models

"Caspian" (45nm SOI, dual-core)

- Tigris platform

- Two AMD K10 cores

- AMD-V, PowerNow!

- Memory support: DDR2 SDRAM (Up to 800 MHz)

- Models: Athlon II M300 to M360

"Champlain" (45nm SOI, dual-core)

- Danube platform

- Two AMD K10 cores

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1333 MHz)

- Models: Athlon II models

Sempron models

"Caspian" (45nm SOI, single-core)

- Tigris platform

- Single AMD K10 core

- AMD-V, PowerNow!

- Memory support: DDR2 SDRAM (Up to 800 MHz)

- Models: Sempron M100 to M140

Turion II Neo models

"Geneva" (45nm SOI, dual-core)

- Nile platform[34][36]

- Two AMD K10 cores

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1066 MHz)

- Models: Turion II Neo models

Athlon II Neo models

"Geneva" (45nm SOI, dual-core)

- Nile platform

- Two AMD K10 cores

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1066 MHz)

- Models: Athlon II Neo models

"Geneva" (45nm SOI, single-core)

- Nile platform

- Single AMD K10 core

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1066 MHz)

- Models: Athlon II K125 and K145

V models

"Geneva" (45nm SOI, single-core)

- Nile platform

- Single AMD K10 core

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1066 MHz)

- Models: V 105

"Champlain" (45nm SOI, single-core)

- Danube platform

- Single AMD K10 core

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1333 MHz)

- Models: V 120 to 160

Phenom II models

"Champlain" (45nm SOI, quad-core)

- Danube platform

- Four AMD K10 cores

- Unlike desktop models, mobile Phenom II models do not have L3 cache

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1333 MHz)

- Models: Phenom II models

"Champlain" (45nm SOI, tri-core)

- Danube platform

- Three AMD K10 cores

- Unlike desktop models, mobile Phenom II models do not have L3 cache

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1333 MHz)

- Models: Phenom II models

"Champlain" (45nm SOI, dual-core)

- Danube platform

- Two AMD K10 cores

- Unlike desktop models, mobile Phenom II models do not have L3 cache

- AMD-V, PowerNow!

- Memory support: DDR3 SDRAM, DDR3L SDRAM (Up to 1333 MHz)

- Models: Phenom II models

Llano APUs

"Sabine" (32nm SOI, dual or quad-core)

- Fabrication 32 nm on GlobalFoundries' SOI process

- Socket FS1

- Two or four upgraded K10 cores codenamed Husky[citation needed] (K10.5[citation needed]) with no L3 cache, and with Redwood-class integrated graphics on die (WinterPark for the dual-core variants and BeaverCreek for the quad-core variants)

- Integrated PCIe 2.0controller

- GPU: TeraScale 2

- Select models support Turbo Core technology for faster CPU operation when the thermal specification permits

- 2.5 GT/s UMI

- AMD-V, PowerNow!

- Support for 1.35 V DDR3memory specified

- Models: Sabine mobile APUs

Server

There are two generations of K10-based processors for servers: Opteron 65 nm and 45 nm.

Successor

AMD discontinued further development of K10 based CPUs after Thuban, choosing to focus on

Family 11h and 12h derivatives

Turion X2 Ultra Family 11h

The Family 11h microarchitecture was a mixture of both K8 and K10 designs with lower power consumption for laptop that was marketed as Turion X2 Ultra and was later replaced by completely K10-based designs.[1]

Fusion Family 12h

The Family 12h microarchitecture is a derivative of the K10 design:[37][38]

- Both CPU and GPU were re-used to avoid complexity and risk

- Distinct Software and Physical integration makes Fusion (APU) microarchitectures different

- Power-saving improvements including clock gating

- Improvements to hardware pre-fetcher

- Redesigned memory controller

- 1MB L2 cache per core

- No L3 cache

- Two new buses for on-die GPU to access memory (called Onion and Garlic interfaces)

- AMD Fusion Compute Link (Onion) – interfaces to CPU cache and coherent system memory (see cache coherence)

- Radeon Memory Bus (Garlic) – dedicated non-coherent interface connected directly to memory

Media discussions

Note: These media discussions are listed in ascending date of publication.

- "AMD CTO speaks about future AMD technologies". AnandTech. 2005-10-14.

- "AMD outlines Future Goals (mostly non-specific at this time)". TechReport. 2005-10-17. Archived from the original on 2006-12-30. Retrieved 2006-08-19.

- "AMD eyes Z-RAM for dense caches". CNet News. 2006-01-20.

- "AMD licenses Z-RAM". SlashDot. 2006-01-21.

- "AMD's K8L to double FPU units in 2007". Geek.com. 2006-02-24. Archived from the original on 2016-01-12. Retrieved 2015-06-07.

- "Rev G. and H. AMD64 chips Preliminary information". The Inquirer. 2006-03-03. Archived from the original on March 12, 2006.

{{cite news}}: CS1 maint: unfit URL (link) - "Interview with Henri Richard (Part 2)". DigiTimes. 2006-03-14.

- "AMD demonstrates Hardware Coprocessor Offload". LinuxElectrons. 2006-03-20. Archived from the original on 2006-10-21.

- "Implementation of FPGA through coherent HTT". The Inquirer. 2006-03-26. Archived from the original on January 12, 2016.

{{cite news}}: CS1 maint: unfit URL (link) - "AMD's K8L 65 nm core due H1 07". Reg Hardware. 2006-04-04. Archived from the original on 2007-05-24. Retrieved 2007-04-19.

- "An AMD Update: Fab 36 Begins Shipments, Planning for 65 nm and AM2 Performance". AnandTech. 2006-04-04.

- "Fab36 substantially converted to 65 nm by mid-2007". AnandTech. 2006-04-04.

- "AMD shows off details of K8L". The Inquirer. 2006-05-16. Archived from the original on June 14, 2006.

{{cite news}}: CS1 maint: unfit URL (link) - "AMD's K8L and 4x4 Preview". RealWorldtech. 2006-06-02.

- "AMD K8L and 4X4 Technologies". ArsTechnica. 2006-06-02.

- "AMD Quad-Core K8L & 4x4 Details". Pure OverClock. 2006-06-03. Archived from the original on February 9, 2012.

- "Socket AM2 Forward Compatible With AM3 CPUs". DailyTech. 2006-07-06. Archived from the original on 2007-06-08.

- "K8L on schedule, due for release as early as Q1 07". The Inquirer. 2006-07-11. Archived from the original on September 6, 2007.

{{cite news}}: CS1 maint: unfit URL (link) - "GNU binutils support for the new K10 instructions". SourceWare.org. 2006-07-13.

- "AMD Executives Confirm K8L to Arrive in Mid-2007". X-bit labs. 2006-07-21. Archived from the original on 2006-11-26.

- "AMD To Demo K8L By Year End". moneycontrol.com. 2006-07-23. Archived from the original on August 18, 2007.

- "AMD intros new Opterons and promises 68 W quad-core CPUs". tgdaily.com. 2006-08-15. Archived from the original on 2006-08-21.

- "Next-Generation AMD Opteron Paves The Way For Quad-Core". crn.com. 2006-08-15. Archived from the original on 2012-02-06. Retrieved 2007-04-19.

- "AMD's Next Generation Microarchitecture Preview: from K8 to K8L". X-bit labs. 2006-08-21. Archived from the original on 2006-08-27.

- "AMD quad cores: the whole story unfolded". The Inquirer. 2006-09-16. Archived from the original on May 19, 2007.

{{cite news}}: CS1 maint: unfit URL (link) - "AMD reinvents the x86". InfoWorld. 2007-02-07. Archived from the original on December 7, 2008.

- "Inside Barcelona: AMD's Next Generation". RealWorldTech. 2007-05-16.

See also

- AMD K9

- Phenom (processor)

- Phenom II

- List of AMD Phenom microprocessors

- List of AMD Athlon X2 microprocessors

References

- ^ a b "List of AMD CPU microarchitectures - LeonStudio". LeonStudio - CodeFun. 3 August 2014. Archived from the original on 26 September 2020. Retrieved 12 September 2015.

- ^ Hesseldahl, Arik (2000-07-06). "Why Cool Chip Code Names Die". forbes.com. Retrieved 2007-07-14.

- ^ "The Inquirer report". The Inquirer. Archived from the original on September 6, 2007.

{{cite web}}: CS1 maint: unfit URL (link) - ^ a b Valich, Theo. "AMD explains K8L misnomer". The Inquirer. Archived from the original on February 10, 2007. Retrieved 2007-03-16.

{{cite news}}: CS1 maint: unfit URL (link) - ^ Official Announcement of "AMD Next Generation Processor Technology"

- ^ Video interview of Giuseppe Amato (AMD's Technical Director, Sales and Marketing EMEA) Archived 2009-07-12 at archive.today in February 2007

- ^ Microprocessor Forum 2003 presentation slide

- ^ AMD's vision for next few years - an interview with Henri Richard

- ^ "AMD Demonstrates Its Quad Core Server Chips". CNET.com. 2006-11-30.

- ^ "AMD Demonstrates Barcelona; The First True, Native Quad Core Opteron". legitreviews.com. 2006-11-30.

- ^ "AMD Expects Quad Core Barcelona to Outperform Clovertown by 40%". dailytech.com. 2007-01-25. Archived from the original on 2007-02-27. Retrieved 2007-04-19.

- ^ "Go to 'Barcelona' over 'Cloverton'". CNET.com. 2007-01-23.

- ^ "TGDaily report". Archived from the original on 2007-09-26. Retrieved 2007-05-11.

- ^ "Understanding AMD's TLB Processor Bug". Daily Tech. Archived 2009-02-18 at the Wayback Machine. December 5, 2007

- ^ "TLB Bug – in the Past". Xbit Labs. Archived 2009-02-09 at the Wayback Machine. March 26, 2008

- ^ "An AMD Update: Fab 36 Begins Shipments, Planning for 65 nm process and AM2 Performance". AnandTech. 2006-04-04.

- ^ "AMD's next-generation Star supports DDR2-1066 & SSE4a". HKEPC Hardware. Retrieved 2007-03-19.

- ^ Shimpi, Anand Lal. "Barcelona Architecture: AMD on the Counterattack". AnandTech. Archived from the original on 19 March 2007. Retrieved 2007-03-18.

- ^ Case, Loyd. "AMD Unveils Barcelona Quad-Core Details". Ziff Davis. Retrieved 2007-03-18.[dead link]

- ^ "AMD Next Generation Processor Technology Slides". HardOCP. 2006-08-22.

- ^ "BIOS and Kernel Developer's Guide (BKDG) For AMD Family 10h Processors" (PDF). p. 24. Archived from the original (PDF) on June 9, 2011. Retrieved 2010-05-29.

Physical address space increased to 48 bits.

- Advanced Micro Devices. June 4, 2013. p. 340. Retrieved January 25, 2015.

- ^ In this article, the conventional prefixes for computer memory denote base-2 values whereby "kilobyte" (KB) = 210 bytes.

- ^ a b c d e f g h i "List of Unlockable AMD CPUs".

- ^ "Legit Reviews - Technology News & Reviews". 27 June 2022.

- ^ Advanced Micro Devices. Archived from the originalon December 2, 2010. Retrieved July 8, 2010.

- ^ Athlon II: Viele neue Exemplare der neuen Einsteiger-Prozessoren von AMD

- ^ In arrivo nuovi processori Athlon II da AMD Archived July 10, 2011, at the Wayback Machine

- ^ "AMD Phenom II X6: Thuban the Dragon". Archived from the original on 2014-07-16. Retrieved 2018-03-29.

- ^ Theo Valich (28 May 2012). "AMD Comes Clean on Transistor Numbers With FX, Fusion Processors". Retrieved 23 August 2013.

- ^ Anand Lal Shimpi (27 September 2012). "AMD A10-5800K & A8-5600K Review: Trinity on the Desktop, Part 1". Retrieved 23 August 2013.

- ^ "AMD launches A-Series and the first 32nm Athlon II X4 CPUs". Retrieved 2013-11-10.

- ^ "The 2009 AMD Mainstream Platform". Amd.com. Archived from the original on 2012-05-27. Retrieved 2014-04-30.

- ^ a b "AMD M880G Chipset". Amd.com. Retrieved 2014-04-30.

- ^ "The 2010 AMD Mainstream Platform". Amd.com. Retrieved 2014-04-30.

- ^ "The 2010 AMD Ultrathin Platform". Amd.com. Archived from the original on 2012-10-31. Retrieved 2014-04-30.

- ^ David Kanter (27 June 2011). "AMD Fusion Architecture and Llano". Real World Tech. Retrieved 12 September 2015.

- ^ Pierre Boudier; Graham Sellers (June 2011). "Memory System on Fusion APUs - The Benefits of Zero Copy" (PDF). AMD Fusion Developer Summit.

External links

- AMD Official Website

- AMD Quad-core processors introduction

- DarkVision Hardware: AMD talks about K9, K10 future innovations

- Next-Generation AMD Opteron Processors Introduced with Record OEM Design Wins and Native Quad-Core Upgrade Path (Official AMD press release on 15 August 2006)

- PC Watch report about K10 based on AMD Technology Analyst Day 2004 and 2005 (in Japanese)

- PC Watch report about K10 based on Slides presented in Microprocessor Forum 2003 (in Japanese)

- "Slides of AMD 2006 Technology Analyst Day: Official Introduction of K10 Microarchitecture" (PDF). Archived from the original on 2009-03-26.

{{cite web}}: CS1 maint: bot: original URL status unknown (link) (2.17 MB) - Software Optimization Guide for AMD Family 10h and 12h Processors

- TechReport: AMD outlines Future Goals

- TweakTown Discussions (2003)

- X-bit labs: AMD K10 Micro-Architecture