PMOS logic

PMOS or pMOS logic (from p-channel

History and application

Compared to the bipolar junction transistor, the only other device available at the time for use in an integrated circuit, the MOSFET offers a number of advantages:

- Given semiconductor device fabrication processes of similar precision, a MOSFET requires only 10% of the area of a bipolar junction transistor.[3]: 87 The main reason is that the MOSFET is self-insulating and does not require p–n junction isolation from neighboring components on the chip.

- A MOSFET requires fewer process steps and is therefore simpler and cheaper to manufacture (one diffusion doping step[3]: 87 compared to four for a bipolar process[3]: 50 ).

- Since there is no static gate current for a MOSFET, the power consumption of an integrated circuit based on MOSFETs can be lower.

Disadvantages relative to bipolar integrated circuits were:

- The switching speed was considerably lower, due to large gate capacitances.

- The high threshold voltage of early MOSFETs led to a higher minimum power-supply voltage (-24 V to -28 V[4]).

A major improvement came with the introduction of

For various reasons Fairchild Semiconductor did not proceed with the development of PMOS integrated circuits as intensively as the involved managers wanted.

By 1972, NMOS technology had finally been developed to the point where it could be used in commercial products. Both Intel (with the 2102)

Description

PMOS circuits have a number of disadvantages compared to the

PMOS uses

The p-channel is created by applying a negative voltage (-25V was common[18]) to the third terminal, called the gate. Like other MOSFETs, PMOS transistors have four modes of operation: cut-off (or subthreshold), triode, saturation (sometimes called active), and velocity saturation.

While PMOS logic is easy to design and manufacture (a MOSFET can be made to operate as a resistor, so the whole circuit can be made with PMOS FETs), it has several shortcomings as well. The worst problem is that there is a direct current (DC) through a PMOS logic gate when the so-called "pull-up network" (PUN) is active, that is, whenever the output is high, which leads to static power dissipation even when the circuit sits idle.

Also, PMOS circuits are slow to transition from high to low. When transitioning from low to high, the transistors provide low resistance, and the capacitive charge at the output accumulates very quickly (similar to charging a capacitor through a very low resistance). But the resistance between the output and the negative supply rail is much greater, so the high-to-low transition takes longer (similar to discharge of a capacitor through a high resistance). Using a resistor of lower value will speed up the process but also increases static power dissipation.

Additionally, the asymmetric input logic levels make PMOS circuits susceptible to noise.[19]

Most PMOS integrated circuits require a power supply of 17-24 volt DC.

Gates

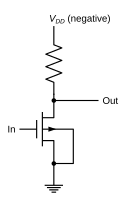

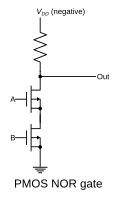

The p-type MOSFETs are arranged in a so-called "pull-up network" (PUN) between the logic gate output and positive supply voltage, while a resistor is placed between the logic gate output and the negative supply voltage. The circuit is designed such that if the desired output is high, then the PUN will be active, creating a current path between the positive supply and the output.

PMOS gates have the same arrangement as NMOS gates if all the voltages are reversed.[22] Thus, for active-high logic, De Morgan's laws show that a PMOS NOR gate has the same structure as an NMOS NAND gate and vice versa.

|

|

|

References

- ^ "1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated". Computer History Museum.

- ISBN 9783540342588.

- ^ OCLC 923116729.

- ^ Mogisters: The New Generation of MOS Monolithic Shift Registers. General Instrument Corp. 1965.

- ^ a b "1964: First Commercial MOS IC Introduced". Computer History Museum. Retrieved 2020-12-07.

- ^ "13 Sextillion & Counting: The Long and Winding Road to the Most Frequently Manufactured Human Artifact in History". Computer History Museum. 2018-04-02. Retrieved 2020-12-08.

- ^ General Instrument MOS Integrated Circuit. General Instrument Microelectronics Division. September 1966.

- ^ M. J. Robles (1968-04-09). New MOS Multiplex Switch is Bipolar Compatible. Fairchild Semiconductor.

- ^ a b c "1968: Silicon Gate Technology Developed for ICs". Computer History Museum. Retrieved 2020-12-11.

- ^ The Intel Memory Design Handbook (PDF). Intel. Aug 1973. Retrieved 2020-12-18.

- ^ ISSN 0018-9219.

- ^ a b c "1970: MOS dynamic RAM Competes with Magnetic Core Memory on Price". Computer History Museum. Retrieved 2020-12-17.

- ^ "Rockwell PPS-4". The Antique Chip Collector's Page. Retrieved 2020-12-21.

- ^ Parallel Processing System (PPS) Microcomputer. Rockwell International. Oct 1974. Retrieved 2020-12-21.

- ^ "A chronological list of Intel products. The products are sorted by date" (PDF). Intel museum. Intel Corporation. July 2005. Archived from the original (PDF) on August 9, 2007. Retrieved July 31, 2007.

- ISBN 9780081020623.

- ^ "1963: Complementary MOS Circuit Configuration is invented". Computer History Museum. Retrieved 2021-01-02.

- ^ Ken Shirriff (December 2020). "Reverse-engineering an early calculator chip with four-phase logic". Retrieved 2020-12-31.

- ISBN 9781466591424. Retrieved 2016-04-10.

Also, the asymmetric input logic levels make PMOS circuits susceptible to noise.

- ^ Fairchild (January 1983). "CMOS, the Ideal Logic Family" (PDF). p. 6. Archived from the original (PDF) on 2015-01-09. Retrieved 2015-07-03.

Most of the more popular P-MOS parts are specified with 17V to 24V power supplies while the maximum power supply voltage for CMOS is 15V.

- ^ "Intel 4004 datasheet" (PDF) (published 2010-07-06). 1987. p. 7. Archived from the original (PDF) on 16 October 2016. Retrieved 2011-07-06.

- ^ Microelectronic Device Data Handbook (PDF) (NPC 275-1 ed.). NASA / ARINC Research Corporation. August 1966. pp. 2–51.

Further reading

- Savard, John J. G. (2018) [2005]. "What Computers Are Made From". quadibloc. Archived from the original on 2018-07-02. Retrieved 2018-07-16.